チップセットとは、マザーボードに装着された2つのチップを示し、ノースブリッジ、サウスブリッジと呼ばれています。

これらのチップは、コンピュータ内部のシステムバスのハブに当たり、データの流れを制御しているコントローラです。

いってみれば、システムバスが道路でデータが車にあたり、チップセットは、交通整理のための信号機になります。

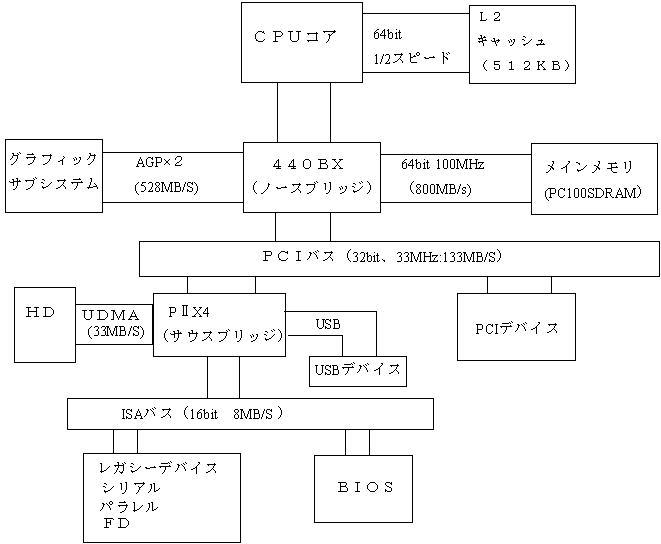

下図は、チップセットと中心としたコンピュータ内部の回路図です。

この図は、440BXチップセットを例にしています。

この際の交通整理の役割を果たすノースブリッジおよびサウスブリッジを総称してチップセットと呼びます。

この制御能力が、コンピュータ全体のパフォーマンスに大きな影響を与えます。

最近では、このチップセットのアーキテクチャがグレードアップする傾向にあります。

例えばCPU-メモリ間、ノースブリッジ-AGP間、またPCIバスの転送レートを向上させることが考えられ、既に実現しつつあります。